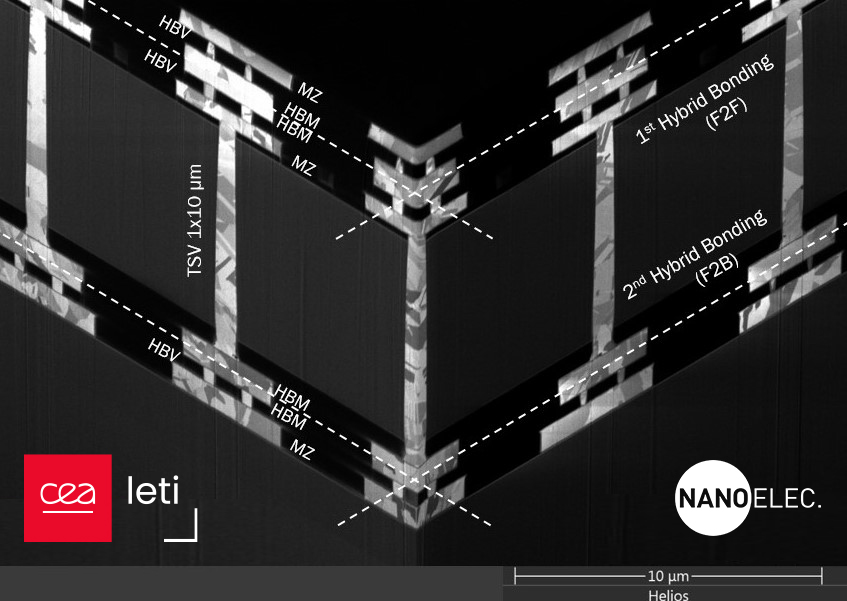

Lors de la conférence internationale IEEE Electronic Components

and Technology (ECTC 2024, USA, mai 2024), les équipes de Nanoelec

ont démontré la faisabilité de la combinaison des technologies de

collage hybride et des connexions traversantes (TSV : Through

Silicon Via) à haute densité. Ces développements sont menés par le

CEA et les entreprises STMicroelectronics, Prophesee, Lynred ,

Siemens EDA dans le cadre du programme Smart Imager de l’IRT

Nanoelec.

L'amélioration du procédé d'amincissement avec un nouvel outil de

meulage a permis de réduire la variation de l’épaisseur totale à

environ 1 μm. Un rendement de connexion électrique de 100 % par

collage hybride et TSV a été démontré.

Depuis plusieurs années, Nanoelec se concentre sur le développement

de briques technologiques nécessaires à la conception et à la

fabrication d’imageurs "trois couches" pour préparer les futures

générations de capteurs d’images intégrant des fonctions de vision

et d’IA embarquée.

Stéphane Nicolas et

Stéphan Borel,

chercheurs au CEA-Leti, présenteront ces

travaux au cours d’un webinaire animé par Eric Ollier (CEA), Directeur du

programme Nanoelec/Smart

Imager.